三星将推出先进的 3D AI 芯片封装技术 SAINT 与台积电竞争

三星电子计划于明年推出一项先进的三维(3D)芯片封装技术,以与代工龙头台积电(TSMC)展开竞争。

总部位于韩国水原市的这家芯片制造商将使用该技术——SAINT(Samsung Advanced Interconnection Technology,三星高级互连技术)——来集成高性能芯片所需的存储器和处理器,包括 AI 芯片,并大幅减小其尺寸。

根据熟悉情况的人士透露,三星计划在 SAINT 品牌下推出三种技术——SAINT S,垂直堆叠 SRAM 存储芯片和 CPU;SAINT D,涉及处理器(如 CPU 和 GPU)和 DRAM 存储器的垂直封装;以及 SAINT L,堆叠应用处理器(APs)。

目前的 2.5D 封装技术在大多数情况下是将不同类型的芯片横向并排组装。

三星的一些新技术,包括 SAINT S,已经通过了验证测试。然而,三星计划在与客户进行进一步测试后,明年推出其商业服务。

封装是半导体制造的最后步骤之一,它将芯片放置在保护壳中以防腐蚀,并提供接口以组合和连接已制造的芯片。

领先的芯片制造商如台积电、三星和英特尔公司正在激烈竞争先进封装技术,该技术集成不同的半导体或垂直连接多个芯片。先进封装技术允许将多个设备合并并作为单一电子设备进行封装。

封装技术可以在不缩小纳米尺寸的情况下通过超精细加工提高半导体性能,这在技术上具有挑战性且需要更多时间。

据咨询公司 Yole Intelligence 预测,全球先进芯片封装市场预计将从 2022 年的 443 亿美元增长到 2027 年的 660 亿美元。在 660 亿美元中,3D 封装预计将占大约四分之一,即 150 亿美元。

台积电:当前 3D 封装领域的领导者

台积电是当前 3D 封装领域的领导者,随着生成式 AI(例如 ChatGPT)等对能够快速处理大量数据的半导体的需求不断增长,这项技术正在迅速增长。

目前行业的主流是 2.5D 封装,它将芯片尽可能地靠近放置以减少数据瓶颈。

全球第一大代工芯片制造商台积电也是全球先进封装市场的领导者,拥有十年历史的 2.5D 封装技术。

台积电正在大量投资测试和升级其 3D 芯片间堆叠技术 SoIC,其客户包括苹果公司和英伟达公司。台积电在 7 月表示,将投资 900 亿新台币(约 29 亿美元)在建立一个新的先进封装工厂。

本月早些时候,联华电子公司(UMC),世界第三大代工厂商,推出了其晶圆对晶圆(W2W)3D IC 项目,以为其客户提供使用硅堆叠技术高效集成存储器和处理器的尖端解决方案。

UMC 表示,其 W2W 3D IC 项目与封装公司如 ASE、Winbond、Faraday 和 Cadence Design Systems 合作,是一项雄心勃勃的计划,旨在利用 3D 芯片集成技术满足边缘 AI 应用的特定需求。

英特尔使用其下一代 3D 芯片封装技术 Foveros 制造先进芯片。

三星的芯片封装路线图

作为世界第二大代工公司,三星自 2021 年推出其 2.5D 封装技术 H-Cube 以来,一直在加速其芯片封装技术的发展。

2.5D 封装技术允许逻辑芯片或高带宽存储器(HBM)堆叠在硅互连器上方,具有较小的尺寸,三星表示。

该韩国公司在 4 月份表示,它正在提供封装一站式服务,处理从芯片生产到封装和测试的整个过程。

三星的新 SAINT 技术旨在提高数据中心和移动 APs 中 AI 芯片的性能,这些 APs 具有设备内 AI 功能,消息人士表示。

超强o1模型智商已超120!1小时写出NASA博士1年代码,最新编程赛超越99.8%选手

o1模型已经强到,能够直出博士论文代码了!来自加州大学欧文分校(UCI)的物理学博士KyleKabasares,实测o1previewmini后发现:自己肝了大约1年的博士代码,o1竟在1小时内完成了。他称,在大约6次提示后,o1便创建了一个运行版本的Python代码,描述出研究论文「方法」部分的内容。站长网2024-09-18 02:33:440000OpenAI CEO和马斯克在线互怼:Grok真能叫板GPT-4吗?

最近,科技界的两大顶流——OpenAICEO和马斯克“掐”起来了。事情的起因是,SamAltman发了一条推文,说“GPTs可以节省很多工作”,配图充满嘲讽意味,直指马斯克的AI聊天机器人Grok。他让GPTBuilder创建一个聊天机器人,以一种“婴儿潮一代令人尴尬的幽默风格”回答问题。站长网2023-11-17 15:32:500001AI公司面临训练数据枯竭危机 高质量数据将在2026年前耗尽

**划重点:**1.🚱**数据枯竭危机:**AI公司可能在不久的将来面临培训数据枯竭的风险,根据研究,高质量文本培训数据可能在2026年耗尽,而低质量文本和图像数据则可能在2030年至2060年之间枯竭。站长网2023-11-14 09:40:110001字节团队提出猞猁 Lynx 模型 多模态 LLMs 开创理解生成新高度

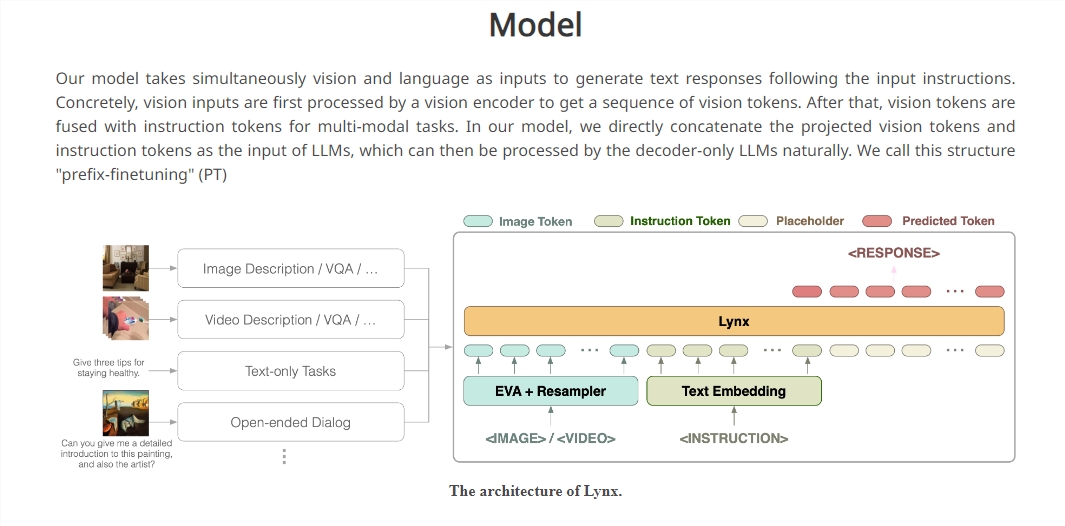

字节团队最近提出了一种名为猞猁(Lynx)的多模态大语言模型(LLMs)。他们通过对二十多种多模态LLMs变体进行系统实验和评估,确定了以prefix-finetuning为主要结构的Lynx模型,并且还提出了一个新的多模态评估基准Open-VQA。论文:https://arxiv.org/abs/2307.02469网站:https://lynx-llm.github.io/站长网2023-07-18 17:22:580000年轻人迷上珍珠直播,开蚌开出的是“泡沫”?

“珍珠有千千万,一颗能定乾坤。姐妹们赶紧跟上节奏。”“想要大珍珠,想要高货,一定要手速快了!”“我们都是直接在珍珠小镇现场选货啊,眼见即可得”……从前两年就火起来的开蚌直播间,到今年冲往诸暨珍珠市场的“背包客”,珍珠的热度一升再升。年轻人们除了爱上黄金,也沉迷于直播间开蚌。站长网2023-11-01 17:43:580000